# Microwave amplifier design

## Assoc. prof. phd. Radu Damian

**Important Note 1.** There is no "magic information" hidden in the middle of this document. You have to go through it step by step without "jumping" in search of the important area.

**Important Note 2.** Even if your experience with digital data has convinced you that an image contains as much information as a thousand pages of text, try not to skip the small black-on-white objects called "letters" between the various pictures in the document.

## 1. Assignment.

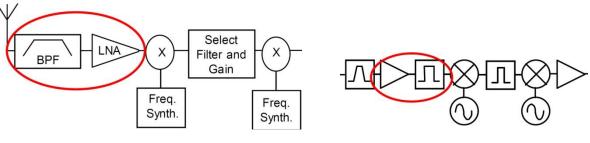

We design the input stage is from an RF receiver, which typically contains one or two bandpass filters and a low noise amplifier. Although the position and number of filters vary, there is generally a filter before the amplifier to limit the bandwidth of the signal applied to it and a filter after the amplifier (figure 1).

Your assignment is a low-noise multi-stage transistor amplifier required to provide a power gain of **G[dB]** and a noise factor of **F[dB]** at the design frequency **f[GHz]**. At the output of the amplifier insert a **N**<sup>th</sup> order bandpass filter with fractional bandwidth of the passband **B[%]** around the design frequency. The amplifier must work with a 50 $\Omega$  source and 50 $\Omega$  load.

The numerical results in this document are for a sample assignment: an amplifier with a gain of (minimum) 20dB, and a noise factor of (maximum) 1dB, at the frequency of 5GHz, followed or preceded by a 4<sup>th</sup> order bandpass filter with fractional bandwidth of the passband of 10%.

# 2. Observations about the assignment data

A few (important) observations about the individual assignment data:

- Even if for certain particular assignments it would be possible to use a single transistor to achieve the required gain, this solution is **not** allowed (multi-stage amplifier), and is generally not recommended because it usually involves designing at the theoretical limit for performance, an approach that backfires during a (eventual) practical implementation.

- Frequency related data (including filter characteristics, bandwidth) must be interpreted absolutely and accurately. The other parameters represent lower performance limits that must be met relatively (from a practical point of view). An amplifier with a higher gain is better, an amplifier with a lower noise is better. As a result, the gain can be targeted (and it is recommended to be) higher than in the assignment, without exaggerating. For example, of all the 20dB amplifiers, the one with a real gain of 22dB will be better, the one with a gain of 25dB will be

even better if it can be obtained with the same investment, but it is useless and impractical to target a gain of 40dB using twice as many components, consuming twice as much power or twice the space on the circuit board.

• Regarding the noise factor, the rule is simple, the smaller the better. For example, of all the 20dB amplifiers in the world, the best is the one with the lowest noise. After choosing the transistor, it also makes great sense to get the lowest possible noise from that transistor. In practice, it is not advisable to choose a more expensive component to exceed the design parameters, even if that component is more efficient, but after a component has been chosen, noise optimization (getting as much performance possible with the same cost) is always useful.

## 3. Separation of the design parameters on the 2 amplification stages

also see: L10/2024, (Friis formula).

We use Friis formula with its main effects:

- it's essential that the first stage is as **noiseless** as possible even if that means sacrificing power gain

- the following stages can be optimized for **power gain** as their noise figure will have a lower influence on the overall noise

$$F_{cas} = F_1 + \frac{1}{G_1} (F_2 - 1) (\text{linear scale!}) \quad G_{cas} = G_1 \cdot G_2 (\text{linear scale}) \text{ or } \quad G_{cas} [dB] = G_1 [dB] + G_2 [dB]$$

For the sample assignment F = 1dB, G = 20dB we can separate the design parameters between the two stages as:

- first/input stage: F1 = 0.7 dB, G1 = 9 dB

- second/output stage: F2 = 1.2 dB, G2 = 13 dB

Remember that we have 2 equations (Friis) and 4 unknowns (F1,G1,F2,G2) so we estimate those unknowns then we check (repeatedly, until correct) that they verify Friis formula:

$$F_{1} = 10^{\frac{F_{1}[dB]}{10}} = 10^{0.07} = 1.175, F_{2} = 10^{\frac{F_{2}[dB]}{10}} = 10^{0.12} = 1.318,$$

$$F_{cas} = F_{1} + \frac{1}{G_{1}} (F_{2} - 1) = 1.215, F_{cas} = 10 \cdot \log(1.215) = 0.846 \, dB$$

$$G_{1} = 10^{\frac{G_{1}[dB]}{10}} = 10^{0.9} = 7.943, G_{2} = 10^{\frac{G_{2}[dB]}{10}} = 10^{1.3} = 19.953,$$

$$G_{cas} = G_{1} \cdot G_{2} = 158.49, G_{cas} = 10 \cdot \log(158.49) = 22 \, dB$$

This choice meets the target for the assignment, with the appropriate reserve/design margin required to account for subsequent problems (additional losses on the lines, the influence of parasitic elements on noise, etc.):

- F = 0.85 dB, G = 22 dB

- $G = G_{design} + \Delta G$

- $F = F_{design} \Delta F$

## 4. Selection of the number of transistor types

The assignment requires that we use at least two transistors for the amplifier, but we must decide whether to use the same transistor type in both stages or to use two different transistor types. The two stages have different requirements which suggests the use of two different types, a low noise transistor, followed by a higher gain transistor (this is the recommended selection that brings an extra point to the project grade). If this is the case we should be looking for two different transistors:

- first/input stage: F1 (max) = 0.7 dB, G1 (min) = 9 dB

- second/output stage: F2 (max) = 1.2 dB, G2 (min) = 13 dB

However, in the current document, the first option is chosen, namely the use of the same transistor for both amplification stages. This is done for concision of the document and to avoid adding a supplemental transistor to the list of prohibited/penalized components (NE 71084, ATF 34143). The transistor we choose must meet requirements for both stages:

• first/second stage: F = min (F1,F2) = 0.7 dB, G = max(G1,G2) = 13 dB

# **5. Selection of the transistor(s)**

also see Lab3 doc/2024 pt. 1

**Important Note 3.** Choosing a suitable transistor is a **<u>time consuming</u>** process, multiple attempts are necessary until the discovery of a suitable component. There is no ideal component usable at any frequency/assignment, forcing the students to apply the selection procedure is the reason behind the existence of the prohibited/penalized components.

The choice of a particular transistor is controlled by its ability to provide the gain and noise factor at the design frequency. The type of transistor is a first parameter that must be estimated. Currently, bipolar Si based transistors have operating frequencies of up to 2-2.4GHz and higher noise, being designed for use in commercial, unpretentious, low power GSM / wireless applications. Unipolar transistors (usually based on GaAs) have higher operating frequencies (ten/tens of GHz), low noise, but are sensitive to overvoltages/overcurrents and are more complicated to control in direct current (bias). However new technologies like Silicon Germanium Carbon (SiGe:C) or Gallium Nitride (GaN) might change this conclusion.

In principle, it is recommended to start from the selection guide (figure 2 - one of the first pages in any written component catalog) as it lists some of the key values of those components. A first step is to select "Low Noise" transistors list, as power transistors, general purpose or pulse operation transistors are not suitable for this design.

| Part<br>Number | Gate Width<br>(µm) | Frequency<br>Range (GHz) | Test Freq.<br>(GHz) | V <sub>dd</sub><br>(V) | l <sub>dd</sub><br>(mA) | NF <sub>o</sub><br>(dB) | G <sub>a</sub><br>(dB) | OIP3<br>(dBm) | P <sub>1 dB</sub><br>(dBm) | Package                |

|----------------|--------------------|--------------------------|---------------------|------------------------|-------------------------|-------------------------|------------------------|---------------|----------------------------|------------------------|

| ATF-33143      | 1600               | 0.45 - 6                 | 2                   | 4                      | 80                      | 0.5                     | 15.0                   | 33.5          | +22                        | SOT-343 (SC-70)        |

| ATF-331M4      | 1600               | 0.45 - 6                 | 2                   | 4                      | 60                      | 0,6                     | 15.0                   | 31            | +19                        | MiniPak <sup>[2]</sup> |

| ATF-34143      | 800                | 0.45 - 6                 | 2                   | 4                      | 60                      | 0.5                     | 17.5                   | 31.5          | +20                        | SOT-343 (SC-70)        |

| ATF-35143      | 400                | 0.45 - 6                 | 2                   | 2                      | 15                      | 0.4                     | 18.0                   | 21            | +10                        | SOT-343 (SC-70)        |

| ATF-38143      | 800                | 0.45 - 6                 | 2                   | 2                      | 10                      | 0.4                     | 16.0                   | 22            | +12                        | SOT-343 (SC-70)        |

| ATF-36077      | 200                | 1.5 - 18                 | 12                  | 1.5                    | 10                      | 0.5                     | 12.0                   | 2 <u>-</u> 1  | +5                         | 70 mil SM              |

| ATE-36163      | 200                | 15-18                    | 12                  | 15                     | 15                      | 12                      | 10.0                   | · · · · · ·   | +5                         | SOT-363 (SC-70)        |

Low Noise pHEMTs (Typical Specifications @ 25°C Case Temperature)

Figure 2

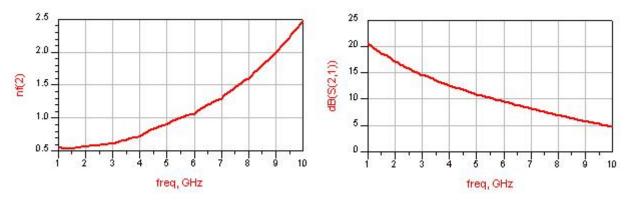

Above is an example of the selection guide for transistors from Agilent/Avago/HP (figure 2). Not all selection guides show the recommended "Frequency Range", but if it exists, the manufacturer's indication may be taken into account. Instead, the "Test Frequency", minimum noise factor (NF<sub>0</sub>), and associated gain ( $G_a$ ) (at that test frequency) are always present. We must remember that the parameters that interest us vary with the frequency, typically the gain expressed in dB decreases linearly with the frequency and the noise factor expressed in dB increases exponentially with the frequency (under normal use conditions – below is the typical variation for ATF 34143: figure 3). Usually, an extrapolation from the test frequency should be made to estimate typical values at the design frequency.

For the sample assignment, we can start from information from the selection guide/datasheet, so from NF = 0.5dB, G = 17.5dB at 2GHz, we can estimate a performance of about NF =  $0.7 \div 0.8$ dB and G = 14÷15dB at 5GHz, at 4V/60mA bias.

**Important Note 4.** Remember that the signal performance strongly depends on the bias point, so it is recommended, after choosing the transistor, to look for the optimal bias point for the current application. Usually low voltage/low current biases offer less noise but also less gain, of course with the decrease of current and power that can be handled by that particular transistor.

It is advisable to obtain (Google) the complete datasheet for the candidate transistor. For example for ATF34143 (Avago) from the datasheet we can extract the following details for operation at 5GHz:

- bias point of 4V Vds, 60mA Ids offers Fmin = 0.67dB, MSG = 15.23dB

- bias point of 3V Vds, 20mA Ids offers Fmin = 0.54dB, MSG = 14.25dB

We choose to continue with a bias point of 3V/20mA Vds/Ids for both amplification stages. In real situations, if increasing the complexity of the bias circuit is not a problem, different bias points for the first and second stages can be chosen.

**Important Note 5.** The fulfillment of separate noise/gain conditions does not necessarily mean that the application as a whole will be fully satisfied. For example, a low noise amplifier involves **simultaneously** fulfilling several conditions: gain/noise/stability/realizability of components needed for impedance matching. It might be necessary to return to the transistor selection phase if later the chosen component proves unsuitable.

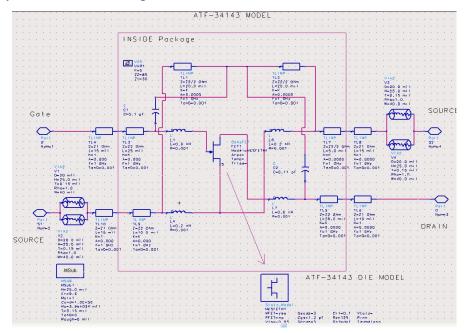

# 6. Model data for transistors

In order to use the transistor in ADS it is necessary to obtain the model data for the transistor. For ATF34143, the complete ADS model of the transistor is available for download (including case parasitics, layout). We will not use this model because:

- Such models are not always available. For Avago ATF34143 this is due to the company's history: HP = HP + Agilent, Agilent = Agilent + Keysight + Avago

- The complete ADS model is an integral component model and in order to be used in the small signal schematic it **must** be properly biased in DC, which goes beyond the scope of the current project assignment. In real situations, however, this would be an advantage (correct modeling of the dependence signal performance/bias).

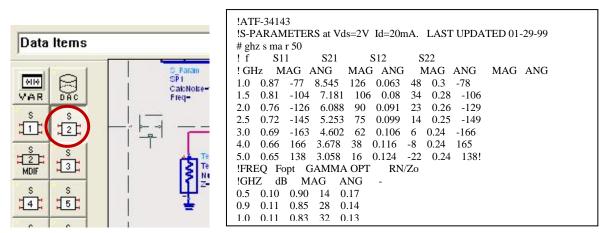

What you really need for a device is the list of S and noise parameters at different frequencies. The values can be obtained from a traditional **datasheet** or can be obtained as ready to use **files** from the manufacturer's **website**. The standard format is called Touchstone and consists of clear text listings of the complex values in the form of a module/argument. The format is not difficult to interpret or modify/create if you cannot find the <u>s2p file</u>. The typical extension for transistors is "\*.s2p" (2 represents the number of ports, a diode will have "\*.s1p" files for example). <u>All</u> RF/microwave components have S-parameter files available on the manufacturers' website or can be easily created from traditional datasheets (copy / paste).

Inserting such a model into ADS is made from the "Data Items" palette, where you choose the two-port component (as in figure 4) which allows inserting an external file in various formats, but the data you usually can find is in Touchstone format (file extension: \*.s2p, internal format: standard ASCII text, cam be opened/modified with Notepad, figure 4).

## Figure 4

**Important Note 6.** For the project assignment it is recommended to check the presence of the noise parameters in the s2p file at the end (as in the previous figure). Not all bias conditions of a low noise transistor are characterized by good noise performance, and some possible bias points will not have the noise data as their typical usage is in the final stages of an multi-stage amplifier where noise is less important and it is possible that for a low noise transistor there are some s2p files lacking the noise data.

# 7. Checking transistor's capabilities

also see Lab3/2024 pts. 4-5

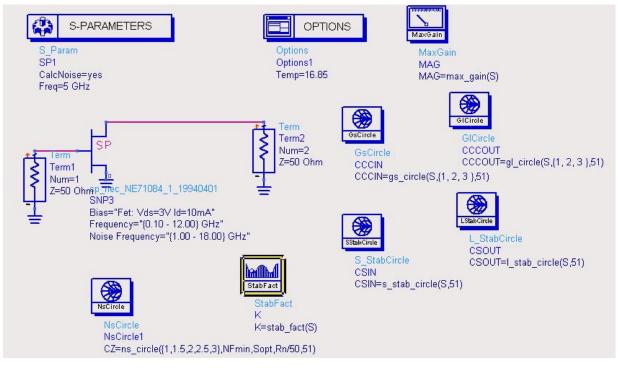

It is recommended that you start with a simple schematic to quickly calculate important parameters for the candidate transistor  $\underline{at}$  your specific design frequency. The first and the second schematics from the lab 3 are a good starting point if they can be recovered.

If you cannot manage to compute in ADS the required parameters, or ADS is not available, the calculation of the parameters of interest can be done manually. It is still necessary to represent the stability, gain, noise circles but there are free programs available on the Internet that can do this:

- Avago Appcad (v4.0: <u>https://www.broadcom.com/appcad</u>)

- Smith Chart (v4.10: <u>http://fritz.dellsperger.net/smith.html</u>)

If you use ADS draw a schematic similar to that in figure 5 (lab 3 pt. 4). The details for drawing the schematic are those from lab 3 and are not repeated here. A common mistake is to perform the analysis with a linear frequency variation, so a minimal check is in the S-Parameters controller, the choice of Single Point analysis, at a frequency equal to the frequency in the individual assignment (5GHz in the sample assignment).

Figure 5

If you don't use ADS to compute the gains available by matching the input/output port of the transistor, then this calculation must be performed manually, those values being necessary to be able to instruct ADS to display the required circles (remember that the circles you request – values between the curly braces  $\{\}$  – depend on the available gains/noise figure for your particular transistor). The modulus of the required S parameters can be very easily read from the S parameter file for 5GHz.

$$G_{0} = |S_{21}|^{2} = 10.017 = 10.007 \, dB$$

$$G_{L \max} = \frac{1}{1 - |S_{22}|^{2}} = 1.051 = 0.215 \, dB, \ G_{S \max} = \frac{1}{1 - |S_{11}|^{2}} = 1.694 = 2.289 \, dB$$

$$G_{TU \max} [dB] = G_{S \max} [dB] + G_{0} [dB] + G_{L \max} [dB] = 12.511 \, dB$$

In the unilateral transistor assumption, we will obtain a maximum gain of 12.51dB by perfect matching the input and output ports (conditions that probably will not be able to be met). The intrinsic gain of 10.01dB of the transistor will be available, but by input matching we will target a gain of less than 2.29dB (0dB, 1dB, 2dB) and an output gain of less than 0.22dB (-2dB, -1dB, 0dB - remember gains can be negative in dB).

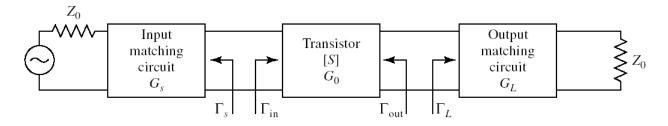

For the design of the matching networks (G<sub>S</sub>, G<sub>L</sub> in figure 7) we will use the method of getting a required reflection coefficient ( $\Gamma_S$ ,  $\Gamma_L$ ) using a series transmission line and a shunt stub, starting from the 50 $\Omega$  source/load, see Lectures7-10/2024, "Impedance Matching with Stubs; Analytical solutions (Exam / Project)".

$$\Gamma = |\Gamma| \cdot e^{j\varphi}, \ \cos(\varphi + 2\theta) = -|\Gamma|, \ \theta_{serie} = \beta \cdot l_s = \frac{1}{2} \cdot \left[\pm \cos^{-1}(-|\Gamma|) - \varphi\right] + k \cdot 180^{\circ}$$

$$\operatorname{Im}[y] = \frac{\mp 2 \cdot |\Gamma|}{\sqrt{1 - |\Gamma|^2}}, \ \theta_{paralel} = \beta \cdot l_P = \tan^{-1} \frac{\mp 2 \cdot |\Gamma|}{\sqrt{1 - |\Gamma|^2}} + k \cdot 180^{\circ}$$

**Important Note 7.** Note the possibility/requirement to add 180° multiples to the electrical lengths of the lines to obtain positive values.

**Important Note 8.** The equation that provides the electrical length of the series line has two solutions. The sign of the chosen solution imposes the sign used in the shunt stub equation. As a result, there will be (only) **two** solutions for a particular match, both with the similar performance.

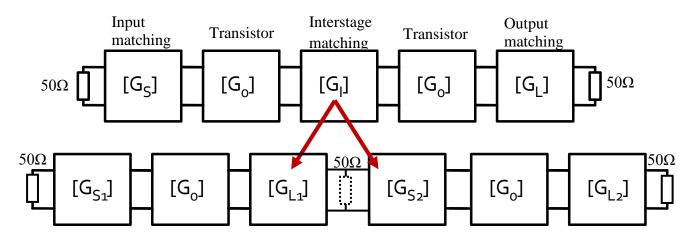

For the interstage matching ( $G_I$  in figure 7) we will use the same method by matching the two amplification stages to one virtual 50 $\Omega$  impedance introduced between the two stages: the output match for the first transistor ( $G_{L1}$ ) provides one 50 $\Omega$  impedance and from this virtual 50 $\Omega$  we design the input match for the second transistor ( $G_{S2}$ ), procedure followed by the unification of the two matching circuits ( $G_{L1} + G_{S2} = G_I$ ).

It is possible to design the amplifier without splitting explicitly the amplifier in two distinct stages (as in figure 7). In this sample procedure we will split the schematic in two stages ( $G_{S1} + G_0 + G_{L1}$  and  $G_{S2} + G_0 + G_{L2}$ ) because it allows us to simulate the two stages independently in order to verify their design, followed by their cascade connection. For alternate method ( $G_{S1} + G_0 + G_I + G_0 + G_{L2}$ ) you can consult the older version (2022 of this example ("Sample Project 2021/2018").

## **8.** Design of the impedance matching for the first stage

As we discussed earlier at pt. 3, in the case of the first amplification stage, it is preferable to favor noise performance by sacrificing (but not too much) the power gain. In order to use the analytical solutions, it is necessary to know an input and output reflection coefficient that meets the desired conditions. The identification of the transmission coefficient needed at the <u>input of the first transistor</u> is done by investigating the circles of stability, gain, noise.

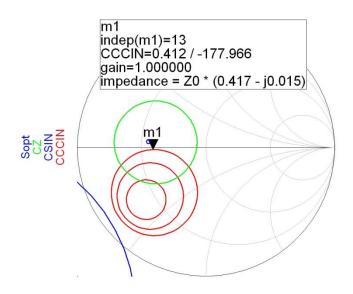

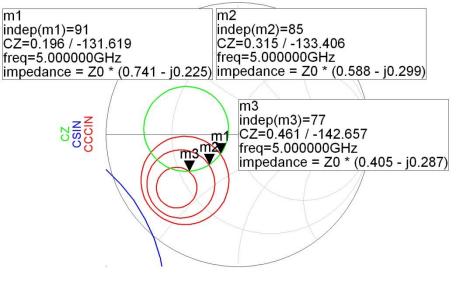

The maximum gain that can be obtained by input matching is 2.29dB (pt. 7, figures 5-6) so we will draw the constant gain circles for 1dB, 1.5dB, 2dB (i.e. "sacrifice"/loss 1.2dB, 0.7dB, 0.2dB). For this, in ADS it is necessary to modify the equation in the component that draws these circles to CCCIN=gs\_circle(S,{1,1.5,2},100) where 100 (or other value) is the number of points on the circle circumference calculated (more will give a better accuracy in positioning the marker on these circles). Draw the noise circle for 0.75dB (close to the 0.7dB required) and the minimum noise point (optimal reflection coefficient for minimum noise figure). The input stability circle **must** also be represented (the noise/gain of the device does not matter if the device is unstable). The result chart for designing the input match of the first stage is plotted in figure 8.

A convenient position is the one indicated with the **m1** marker in figure 8, positioning the marker on the 1dB gain circle meaning decreasing with 1.2dB the achievable gain, but this position is well inside the 0.75dB noise circle (actually close to the minimum noise point, so we can expect a noise factor close to the minimum of 0.54dB) and away from the circle stability. In this position we can read in ADS from the marker legend the value of the reflection coefficient we need to obtain ( $0.412 \angle -178^\circ$ ,  $|\Gamma_{S1}| = 0.412$ ,  $\varphi_{S1} = -178^\circ$ ). If you consider that another position might be better suited for the design, the circles that are actually displayed must be modified (different gain and noise circles, by changing the parameters of the gs\_circle and ns\_circle functions) to have a circle that passes exactly through the desired position (the marker can only be applied to an existing curve). If you use other software the display might be different (usually the instantaneous position of the mouse cursor is displayed near the chart).

Figure 8

$$\cos(\varphi_{S1}+2\theta) = -|\Gamma_{S1}|, \operatorname{Im}[y_{S1}(\theta)] = \frac{\pm 2 \cdot |\Gamma_{S1}|}{\sqrt{1-|\Gamma_{S1}|^2}}$$

| Equation                                                                                                                                           | Solution S1A | Solution S1B |  |  |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------|--------------|--------------|--|--|--|

| $\left( arphi_{S1}+2	heta ight)$                                                                                                                   | +114.33°     | -114.33°     |  |  |  |

| $\theta_{serie} = \frac{1}{2} \cdot \left[ \pm \cos^{-1} \left( - \left  \Gamma_{S1} \right  \right) - \varphi_{S1} \right] + k \cdot 180^{\circ}$ | 146.2°       | 31.8°        |  |  |  |

| $\operatorname{Im}[y_{S1}(\theta)] = \frac{\mp 2 \cdot  \Gamma_{S1} }{\sqrt{1 -  \Gamma_{S1} ^2}}$                                                 | -0.904       | +0.904       |  |  |  |

| $\theta_{paralel} = \tan^{-1} \frac{\mp 2 \cdot  \Gamma_{S1} }{\sqrt{1 -  \Gamma_{S1} ^2}} + k \cdot 180^{\circ}$                                  | 137.9°       | 42.1°        |  |  |  |

| Table 1                                                                                                                                            |              |              |  |  |  |

Table 1

Applying the formulas we get the two analytical solutions for the input (source) match of the first stage: solutions S1A and S1B in table 1.

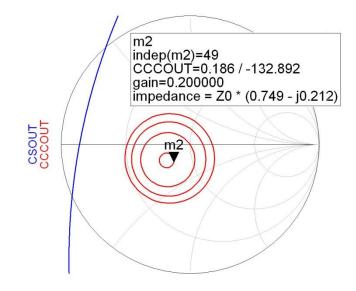

The identification of the transmission coefficient needed at the <u>output of the first transistor</u> is done by investigating the stability and gain circles (the noise introduced by the first transistor is not influenced in any way by its output match). Because noise is not an issue, output match can aim to optimize gain. The maximum gain that can be obtained by output matching is 0.22dB (pt. 7, figures 5-6) so we will draw the constant gain circles for 0.2dB, 0dB, -0.2dB, -0.4dB (i.e. "sacrifice"/loss of 0.02dB, 0.22dB, 0.42dB, 0.62dB). For this, in ADS it is necessary to modify the equation in the component that draws these circles CCCOUT=gl\_circle(S,{-0.4,-0.2,0,0.2},100). The result chart for designing the output match of the first stage is plotted in figure 9.

#### Figure 9

A convenient position is the one indicated with the **m2** marker in figure 9, positioning the marker on the 0.2dB gain circle meaning a gain close to the maximum, far from the stability circle (there is no need to sacrifice gain to improve stability). Note that the 0dB gain circle passes through the center of the Smith Chart (<u>always</u>) so an honorable behavior (0.22dB gain loss) can be obtained without output matching (direct connection of the transistor to  $50\Omega$  - solution that is not generally recommended, the flexibility of the schematic is lost, we eliminate two lines which can be adjusted to correct certain deficiencies). In the m2 position we can read in ADS marker legend the value of the reflection coefficient we need ( $0.186 \angle -132.9^\circ$ ,  $|\Gamma_{L1}| = 0.186$ ,  $\varphi_{L1} = -132.9^\circ$ ).

$$\cos(\varphi_{L1} + 2\theta) = -|\Gamma_{L1}|, \operatorname{Im}[y_{L1}(\theta)] = \frac{\mp 2 \cdot |\Gamma_{L1}|}{\sqrt{1 - |\Gamma_{L1}|^2}}$$

| Equation                                                                                                                                           | Solution L1A | Solution L1B |  |  |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------|--------------|--------------|--|--|--|

| $\left( arphi_{L1} + 2 	heta  ight)$                                                                                                               | +100.72°     | -100.72°     |  |  |  |

| $\theta_{serie} = \frac{1}{2} \cdot \left[ \pm \cos^{-1} \left( - \left  \Gamma_{L1} \right  \right) - \varphi_{L1} \right] + k \cdot 180^{\circ}$ | 116.8°       | 16.1°        |  |  |  |

| $\operatorname{Im}[y_{L1}(\theta)] = \frac{\mp 2 \cdot  \Gamma_{L1} }{\sqrt{1 -  \Gamma_{L1} ^2}}$                                                 | -0.379       | +0.379       |  |  |  |

| $\theta_{paralel} = \tan^{-1} \frac{\mp 2 \cdot  \Gamma_{L1} }{\sqrt{1 -  \Gamma_{L1} ^2}} + k \cdot 180^{\circ}$                                  | 159.3°       | 20.7°        |  |  |  |

| Table 2                                                                                                                                            |              |              |  |  |  |

Applying the formulas we get the two analytical solutions for the output (load) match of the first stage: solutions L1A and L1B in table 2.

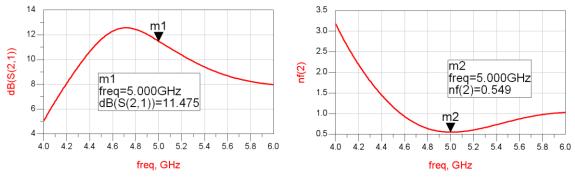

We can perform the simulation of the first amplifier stage to check the validity of the numerical results in Tables 1 and 2. We can choose any of the 4 possible combinations (S1A or S1B and L1A or L1B). We estimate from the chosen circles to obtain a gain  $G = G_{S1} + G_0 + G_{L1} = 1dB + 10dB + 0.22dB$  = 11.22dB, higher than the required 9dB value (pt. 3) so we will have an additional reserve for the second

stage. Regarding the noise, we notice in figure 8 that the chosen position is very close to the minimum noise position ( $\Gamma_{opt}$ ) so we can expect to get quite close to the minimum noise figure of 0.54dB (lower therefore better than the value of 0.7 dB used in pt. 3 estimation).

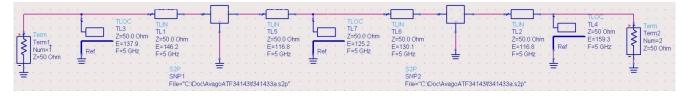

For example, we will choose for simulation the combination of S1A (table 1) with L1A (table 2), resulting in the schematic in figure 10.

| 1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1 | TLIN     TLIN     TLOC       TL1     TL2     TL4       2=50.0 Ohm     Z=50.0 Ohm     Z=50.0 Ohm       E=148.2     E=116.8     E=159.3       F=5.GHz     F=5.GHz     Ref |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| · · <del>_</del> · · · · · · · · · · · · · · · · · · ·                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | · · · · · · · · · · · · · · · · · · ·                                                                                                                                   |  |

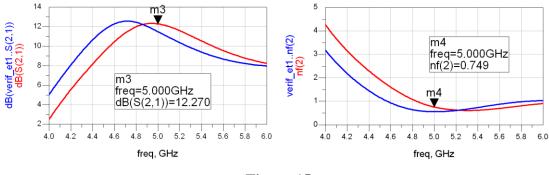

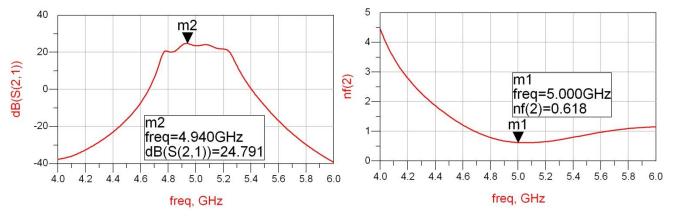

Simulating schematic in figure 10, we obtain the results in figure 11 which correspond to the expected values (the small differences come from the use of the unilateral model for the transistor and are unavoidable, this is one of the reasons why the design must include appropriate reserve/design margin – pt. 3)

## 9. Design of the impedance matching for the second stage

For the match of the <u>input of the second transistor</u> towards the virtual  $50\Omega$  impedance, we will have a similar situation with the input match of the first transistor, but this time the noise is not as important (Friis formula shows that a noise factor of even of 1dB is acceptable), so we will have greater flexibility in choosing the point/marker on the chart (reflection coefficient at the input of the second transistor). We favor positions that will allow the higher gain required for the second stage. As the same transistor is used for the second stage, the Smith chart will look quite similar to figure 8. Figure 12 show the chart with the constant gain circles for 1dB, 1.5dB, 2dB and the noise circle for 0.75dB.

We will be able to choose the position indicated by the marker **m3** in figure 12 ( $0.461 \angle -142.66^{\circ}$ ,  $|\Gamma_{S2}| = 0.461$ ,  $\varphi_{S2} = -142.66^{\circ}$ ) which offers a gain of 2dB by input matching and a small noise (0.75dB, lower therefore better than the value of 1dB from pt. 3). In order to increase the gain by another 0.29dB (maximum possible), it would be necessary to approach the circle of stability (not recommended) and leaving the 0.75dB noise circle therefore increasing the noise of the second stage, an alternative that in the current case is not justified (remember that the required gain is 20dB from which 11.4dB is obtained on the first stage – pt. 8, increasing the gain towards the limit with the sacrifice of other characteristics

is not necessary). If we later encounter stability problems we can try to improve it by choosing another point (for example m1, farther from the stability circle but with a gain reduced by 1dB).

Figure 12

| $\operatorname{Im}[y_{s2}(\theta)] =$ | $\mp 2 \cdot  \Gamma_{S2} $             |

|---------------------------------------|-----------------------------------------|

| $\lim_{y \to 2} y_{s_2}(v) = 0$       | $\sqrt{1 - \left \Gamma_{S2}\right ^2}$ |

| Equation                                                                                                                                           | Solution S2A | Solution S2B |

|----------------------------------------------------------------------------------------------------------------------------------------------------|--------------|--------------|

| $\left( arphi_{S2}+2	heta ight)$                                                                                                                   | +117.45°     | -117.45°     |

| $\theta_{serie} = \frac{1}{2} \cdot \left[ \pm \cos^{-1} \left( - \left  \Gamma_{S2} \right  \right) - \varphi_{S2} \right] + k \cdot 180^{\circ}$ | 130.1°       | 12.6°        |

| $\operatorname{Im}[y_{S2}(\theta)] = \frac{\mp 2 \cdot  \Gamma_{S2} }{\sqrt{1 -  \Gamma_{S2} ^2}}$                                                 | -1.039       | +1.039       |

| $\theta_{paralel} = \tan^{-1} \frac{\mp 2 \cdot  \Gamma_{s2} }{\sqrt{1 -  \Gamma_{s2} ^2}} + k \cdot 180^{\circ}$                                  | 133.9°       | 46.1°        |

Table 3

Applying the formulas we get the two analytical solutions for the input (source) match of the second stage: solutions S2A and S2B in table 3.

For the output (load) match of the second stage, because we use the same transistor ATF34143, the situation will be identical to that in figure 9, with the same importance given to the gain. As a result, we get in in table 4 identical results to those in table 2.

As for pt. 8 we can perform the simulation of the second amplifier stage to check the validity of the numerical results in Tables 3 and 4. We can choose any of the 4 possible combinations (S2A or S2B and L2A or L2B). We estimate from the chosen circles to obtain a gain  $G = G_{S1} + G_0 + G_{L1} = 2dB + 10dB + 0.22dB = 12.22dB$ , slightly lower than the 13dB value used at pt. 3. On the other hand, for the first stage we estimated and verified by simulation a gain of 11.2dB, thus the current solution would obtain a compound gain of 11.2dB + 12.2dB = 23.4dB higher and therefore better than the 22dB value (which included the reserve/design margin) estimated at pt. 3. Regarding the noise, we notice in figure

12 the positioning on the 0.75dB noise circle so this is the estimated noise value (lower therefore better than the 1dB value used in pt. 3 estimation).

| $\sqrt{2}$ $ 2L_2 $                                                                                                                                |              |              |  |  |  |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------|--------------|--------------|--|--|--|--|

| Equation                                                                                                                                           | Solution L2A | Solution L2B |  |  |  |  |

| $\left( arphi_{L2} + 2 	heta  ight)$                                                                                                               | +100.72°     | -100.72°     |  |  |  |  |

| $\theta_{serie} = \frac{1}{2} \cdot \left[ \pm \cos^{-1} \left( - \left  \Gamma_{L2} \right  \right) - \varphi_{L2} \right] + k \cdot 180^{\circ}$ | 116.8°       | 16.1°        |  |  |  |  |

| $\operatorname{Im}[y_{L2}(\theta)] = \frac{\mp 2 \cdot  \Gamma_{L2} }{\sqrt{1 -  \Gamma_{L2} ^2}}$                                                 | -0.379       | +0.379       |  |  |  |  |

| $\theta_{paralel} = \tan^{-1} \frac{\mp 2 \cdot  \Gamma_{L2} }{\sqrt{1 -  \Gamma_{L2} ^2}} + k \cdot 180^{\circ}$                                  | 159.3°       | 20.7°        |  |  |  |  |

|                                                                                                                                                    | Table 4      |              |  |  |  |  |

| $\cos(\varphi_{L2}+2\theta)=- \Gamma_{L2} ,$ | $\operatorname{Im}[y_{L2}(\theta)] = \frac{\mp 2 \cdot  \Gamma_{L2} }{\sqrt{1 -  \Gamma_{L2} ^2}}$ |

|----------------------------------------------|----------------------------------------------------------------------------------------------------|

|----------------------------------------------|----------------------------------------------------------------------------------------------------|

| Table | 4 |

|-------|---|

|-------|---|

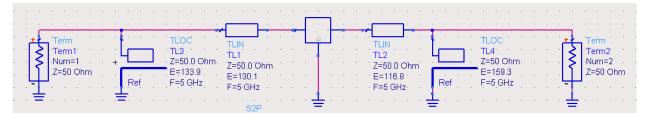

For example, we will choose for simulation the combination of S2A (table 3) with L2A (table 4), resulting in the schematic in figure 13.

### Figure 13

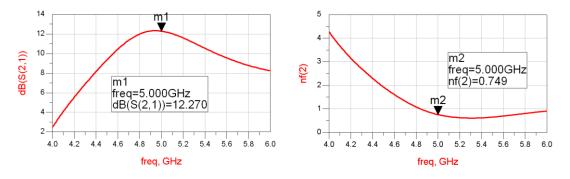

Simulating schematic in figure 13, we obtain the results in figure 14 which correspond to the expected values thus validating computations in tables 3 and 4.

Comparing the results for the first and second stage (figure 15) it is possible to observe, even when using the same type of transistor, compliance with the conclusions derived from Friis' formula in pt. 3: the first stage has a lower noise with the consequence of a lower gain, the second stage has a higher gain to compensate resulting in a higher noise.

Figure 15

#### **10.** Design of the interstage impedance match

In the case of the cascade connection of amplifier stages in figures 10 and 13, the shunt opencircuited lines from the output of the first stage  $(159.3^{\circ})$  and the input of the second stage  $(133.9^{\circ})$  would be connected in parallel. Remember that an open-circuited line represents a pure imaginary admittance. As a result, the two shunt stubs can be replaced by a single stub offering an admittance equal to the sum of the two previous admittances (parallel connection). Attention! the admittances of the lines add up, not the corresponding electrical lengths of the lines.

If we want to design the amplifier without the split simulation of the two amplifier stages (pts. 8 and 9) it is possible that in tables 2 and 3 computation we don't compute the final value (the shunt stub electrical length), as only the previous values (the pure imaginary admittances) are required, to be added for the equivalent shunt stub.

$$Im[y_{L1}(\theta_{L1})] = \frac{\mp 2 \cdot |\Gamma_{L1}|}{\sqrt{1 - |\Gamma_{L1}|^2}} Im[y_{S2}(\theta_{S2})] = \frac{\mp 2 \cdot |\Gamma_{S2}|}{\sqrt{1 - |\Gamma_{S2}|^2}}$$

$$Im[y_{50\Omega}] = Im[y_{L1}(\theta_{L1})] + Im[y_{S2}(\theta_{S2})] = \frac{\pm 2 \cdot |\Gamma_{L1}|}{\sqrt{1 - |\Gamma_{L1}|^2}} + \frac{\pm 2 \cdot |\Gamma_{S2}|}{\sqrt{1 - |\Gamma_{S2}|^2}},$$

$$\theta_{paralel} = \tan^{-1}Im[y_{50\Omega}] + k \cdot 180^{\circ}$$

Because for each matching network we have two distinct solutions with the same modulus but opposite (+/–) signs for the admittance, there will be 4 distinct possibilities of combining the two matching networks. For each combination, the value of the series line's electrical length ( $\theta_{L1}$  and  $\theta_{S2}$ ) is kept for each matching network, the corresponding admittance values are added (pay attention to the sign of each admittance!) and using the tan<sup>-1</sup>() function we compute the electrical length of the equivalent shunt stub. If the value is negative, add 180°.

For example, in table 5 combining solutions L1A and S2A, the values of the series lines  $\theta_{L1} = 116.8^{\circ}$  and  $\theta_{S2} = 130.1^{\circ}$  are kept, add corresponding Im[y] = (-0.379) + (-1.039) = -1.418, the electrical length for the equivalent shunt stub is  $\theta_{paralel} = \tan^{-1}[-1.418] = -54.8^{\circ} (+180^{\circ}) = 125.2^{\circ}$ .

|              |                                        | Solution S2A                                 | Solution S2B                                 |  |

|--------------|----------------------------------------|----------------------------------------------|----------------------------------------------|--|

|              |                                        | $\operatorname{Im}[y_{S2}(\theta)] = -1.039$ | $\operatorname{Im}[y_{S2}(\theta)] = +1.039$ |  |

|              |                                        | $\theta_{S2} = 130.1^{\circ}$                | $\theta_{S2} = 12.6^{\circ}$                 |  |

|              |                                        | $\theta_{L1} = 116.8^{\circ}$                | $\theta_{L1} = 116.8^{\circ}$                |  |

|              | $\mathrm{Im}[y_{L1}(\theta)] = -0.379$ | $Im[y_{50\Omega}] = -1.418$                  | $Im[y_{50\Omega}] = +0.66$                   |  |

| Solution L1A | $\theta_{L1} = 116.8^{\circ}$          | $\theta_{paralel}$ =125.2°                   | $\theta_{paralel} = 33.4^{\circ}$            |  |

|              |                                        | $\theta_{S2} = 130.1^{\circ}$                | $\theta_{S2} = 12.6^{\circ}$                 |  |

|              |                                        | $\theta_{L1} = 16.1^{\circ}$                 | $\theta_{L1} = 16.1^{\circ}$                 |  |

|              | $\mathrm{Im}[y_{L1}(\theta)] = +0.379$ | $\mathrm{Im}[y_{50\Omega}] = -0.66$          | $Im[y_{50\Omega}] = +1.418$                  |  |

| Solution L1B | $\theta_{L1} = 16.1^{\circ}$           | $\theta_{paralel}$ =146.6°                   | $\theta_{paralel} = 54.8^{\circ}$            |  |

|              |                                        | $\theta_{S2} = 130.1^{\circ}$                | $\theta_{S2} = 12.6^{\circ}$                 |  |

| Table 5      |                                        |                                              |                                              |  |

Table 5

# **<u>11. Draw and simulate the complete amplifier</u>**

For the implementation of the amplifier, one of the possible solutions must be chosen for each matching network. In principle, too short lines will be difficult to implement and will physically bring various devices/stubs nearby leading to unwanted coupling so they should be avoided, while too long lines will take up too much (unnecessary) space on the circuit board. All characteristic impedances are equal to  $Z_0 = 50\Omega$

- for input matching we choose solution S1A, order from input to output:

- shunt stub with  $E = 137.9^{\circ}$

- $\circ$  series line with E = 146.2°

- for interstage matching we choose solution L1A/S2A, order from input to output:

- series line with  $E = 116.8^{\circ}$

- $\circ$  shunt stub with E = 125.2°

- $\circ$  series line with E = 130.1°

- for output matching we choose solution L2A, order from input to output:

- $\circ$  series line with E = 116.8°

- shunt stub with  $E = 159.3^{\circ}$

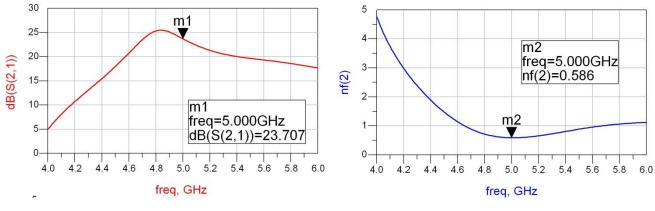

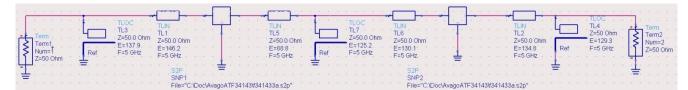

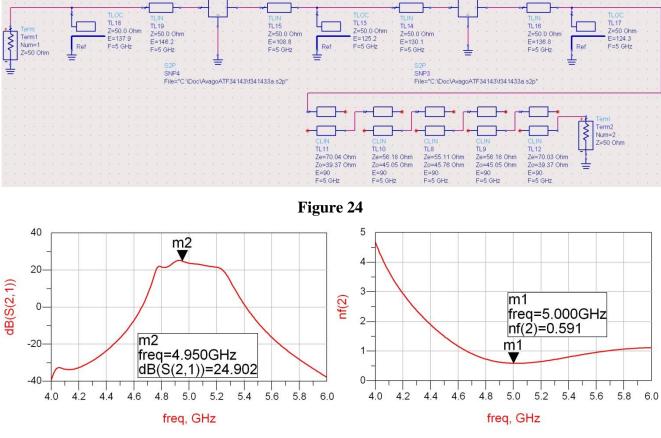

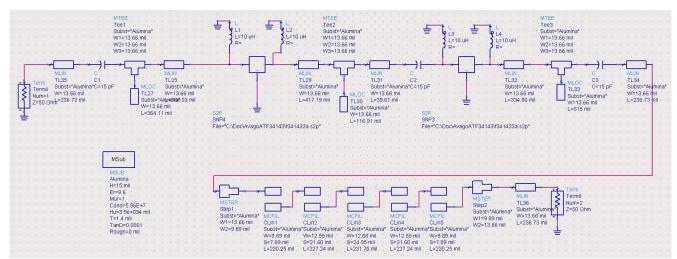

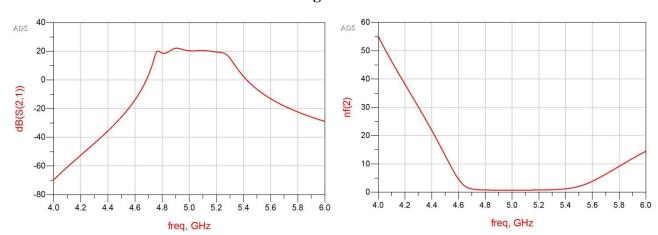

It is the first time we can draw the complete schematic (figure 16) and obtain the final check for previous computations (as in: we obtain the expected gain/noise factor – figure 17).

Figure 16

# **12. Balance the amplifier gain**

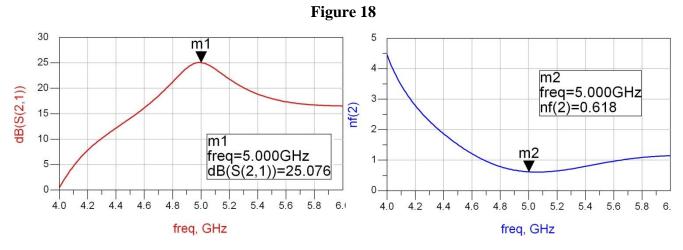

The gain and noise results meet the requirements of the sample assignment with a sufficient reserve for the gain and a noise factor very close to the minimum (much smaller, so better than a noise factor F = 0.85dB initially estimated). The only problem is that the amplifier does not have the maximum gain at 5GHz, which will unbalance the final result.

We want to move the peak of the gain to 5GHz, if possible without affecting the gain and noise factor. It is preferable to adjust the components (electrical lengths of the lines in figure 18) starting from the output to the input because in this way the noise factor is not at all influenced (output matching network) or is less influenced (interstage matching network). If this is not possible without the excessive impact over the power gain only then, **as a last resort**, the two input lines can also be adjusted.

Following the adjustment, balancing can be achieved in the sample assignment by adjusting the lengths of the output lines and one of the lines in the interstage network, with only minor effect (slight increase) on the noise factor in figure 19.

Figure 19

## **13. Design of the passband filter**

#### also see L12/2024

The first step in filter design is to choose the technology. In order to maintain the advantage of using lines instead of lumped elements (2p) it is preferred to use a filter implemented with transmission lines. We will design a coupled-line filter. However, remember that there is a bonus for using a different filter type, so you could investigate filters with capacitively coupled series resonators or with lines as resonators.

For the bandpass filter with coupled lines we have the design relations:

$$Z_0 \cdot J_1 = \sqrt{\frac{\pi \cdot \Delta}{2 \cdot g_1}} \qquad Z_0 \cdot J_n = \frac{\pi \cdot \Delta}{2 \cdot \sqrt{g_{n-1} \cdot g_n}}, n = \overline{2, N} \qquad Z_0 \cdot J_{N+1} = \sqrt{\frac{\pi \cdot \Delta}{2 \cdot g_N \cdot g_{N+1}}}$$

$$Z_{0o,n} = Z_0 \cdot \left[1 - J_n \cdot Z_0 + (J_n \cdot Z_0)^2\right] \qquad Z_{0e,n} = Z_0 \cdot \left[1 + J_n \cdot Z_0 + (J_n \cdot Z_0)^2\right] \qquad n = \overline{1, N+1}$$

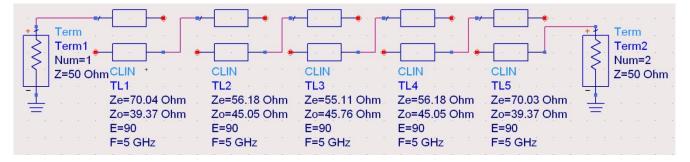

We choose a 4th order equal-ripple filter, with 0.5dB ripple, coefficients from the corresponding table in lectures. The bandpass 4th order filter with coupled lines will be implemented with 5 sections of coupled lines (bandwidth 10%,  $\Delta$ =0.1 – table 6).

| n         | gn     | Z <sub>0</sub> J <sub>n</sub> | <b>Z</b> <sub>0e</sub> [Ω] | Ζ <sub>00</sub> [Ω] |  |

|-----------|--------|-------------------------------|----------------------------|---------------------|--|

| 1         | 1.6703 | 0.306664                      | 70.04                      | 39.37               |  |

| 2         | 1.1926 | 0.111295                      | 56.18                      | 45.05               |  |

| 3         | 2.3661 | 0.09351                       | 55.11                      | 45.76               |  |

| 4         | 0.8419 | 0.111294                      | 56.18                      | 45.05               |  |

| 5         | 1.9841 | 0.306653                      | 70.03                      | 39.37               |  |

| Tabelul 6 |        |                               |                            |                     |  |

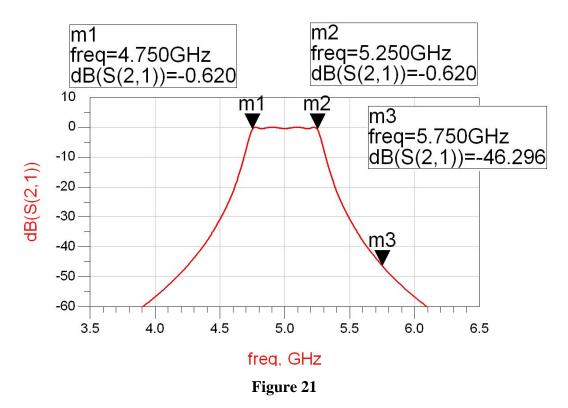

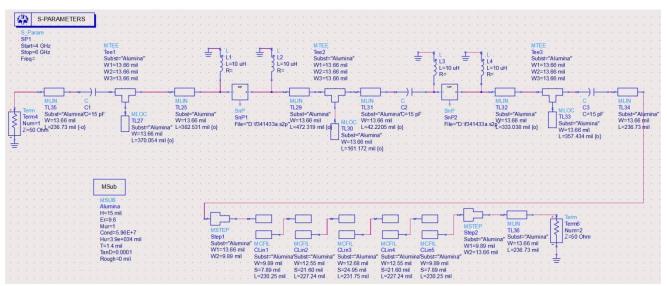

We can verify the filter in a separate schematic (figure 20) with result in figure 21. Check with care the passband as it is an important design parameter.

Choosing a different type for the filter (other than coupled-lines filter as in current example) can bring an additional point for the project grade.

**Important Note 9.** Remember (see also lectures for filters chapter) that for even-order and equal-ripple filters the termination impedance is different from 50 $\Omega$ . In these cases, for certain types of filters, it is necessary to insert a quarter-wavelength transformer. This is not the case with the design relationships for the coupled-line filter where the last section takes into account the coefficient g5 = 1.9841 and treats the last section (Z0×J5) separately to achieve the 50 $\Omega$  impedance matching.

# 14. Final schematic

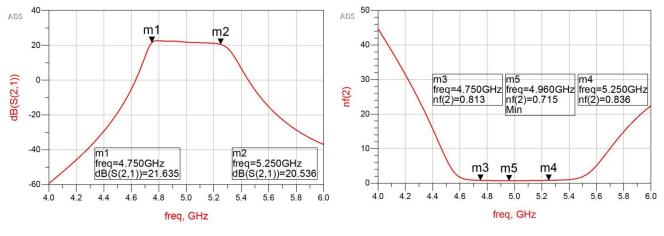

Figure 22

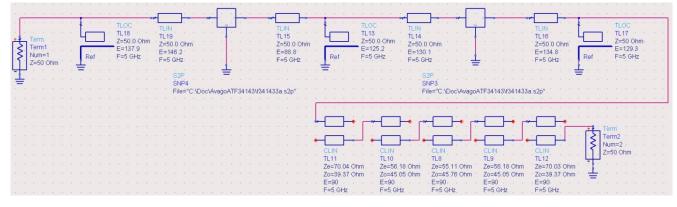

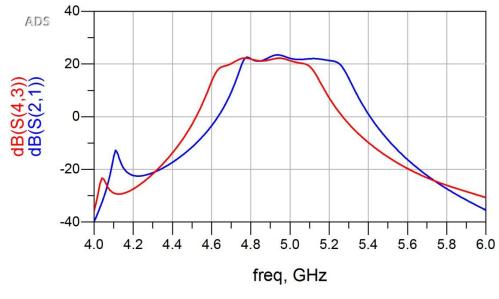

For the final schematic, the amplifier and the filter are connected together (figure 22). The filter can be connected before or after the amplifier.

The only problem with the final schematic results (figure 23) is that at low frequencies at the end of the passband (~4.75GHz) we have a decrease of the gain, below or at least very close to the minimum design gain. This can be compensated by a final adjustment of the transmission lines, preferably with the adjustment of the line in the interstage matching network, whose adjustment altered the noise factor.

After the final tune (figure 24), a slightly better noise factor is obtained (F = 0.591dB) and a power gain with a ripple of approximately 3dB in the bandwidth, between 4.75GHz and 5.25GHz, with a minimum of 21.6dB and a maximum of 24.9dB (figure 25).

The above schematic corresponds to project assignment graded with 10 (if transistors other than those prohibited/penalized are used). The final remark is that in real situations the discussion would not be complete without the analysis of stability and possibly forcing the stability of the circuit (see L9/2024)

# **15. Additional points**

Two additional points can be obtained by unconditionally stabilizing the transistors in wideband, by inserting resistors in series and/or parallel, at the input and/or output of the two transistors. Attention, this procedure will lead to significant degradation of the gain and noise performance of the transistors, and this must be taken into account from the beginning of the design (pt. 5: the transistors will have to be chosen much better than the theme needs, for a significantly larger reserve/design margin to compensate by the degradation brought about by unconditional stabilization).

One additional point can be obtained if two different transistors are used for the two amplifier stages (chosen accordingly: low noise for the first stage, high gain for the second stage). For this additional point, the situation where the same component is used but with different bias conditions is accepted (such as for example ATF34143 at a bias of 3V Vds, 20mA Ids, Fmin = 0.54dB, MSG = 14.25dB for the first stage and ATF34143 at a bias of 4V Vds, 60mA Ids, Fmin = 0.67dB, MSG = 15.23dB for the second stage). The important thing is that the two bias conditions are characterized by different S parameter files, so different small signal models.

Another additional point can be obtained if you use a different type for the filter than coupled lines filter.

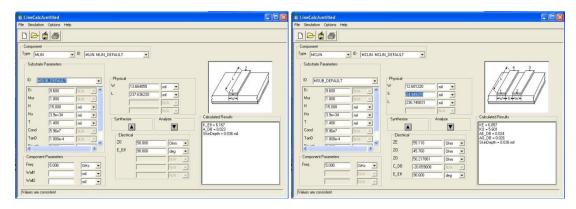

The implementation of the lines in microstrip technology (figure 26), microstrip line models **and** the modeling of transition blocks between various lines (MTEE, MSTEP) can bring up to two extra points. You will have to use the ADS tool Linecalc (figure 27) or an online equivalent.

| MTEE           Tee1           Subst="Alumina"           W1=13.66 mil           W2=13.66 mil           W3=13.66 mil | MTEE         MTEE           Tee2         Tee3           Subst="Alumina"         Subst="Alumina"           W1=13.66 mil         W1=13.66 mil           W2=13.66 mil         W2=13.66 mil           W3=13.66 mil         W3=13.66 mil                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|--------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Term4<br>Num=3<br>Z=50 Ohm Subst="Alumina"<br>W=13.66 mil<br>L=364.11 mil                                          | MLIN         MLIN <th< td=""></th<>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| маланан каланан каланан каланан калан к    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| MSUB<br>Alumina<br>H=15 mil                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| H=15 mil<br>Er=9.6<br>Mur=1<br>Cond=5.96E+7<br>Hu=3.99+034 mil<br>T=1.4 mil<br>TanD=0.0001<br>Rough=0 mil          | Image: Constraint of the second se |

Figure 26

Figure 27

Instead of the coupled line microstrip model (MCLIN), you should use the coupled line filter section model (MCFIL in figure 26), a more accurate model than MCLIN because it takes into account that two successive sections are physically joined. Investigating the results (figure 28), there is a shift of the transfer function (red) towards lower frequencies than the ideal models (blue) due to the MCFIL/MCLIN difference. The correction of this shift is done by a slight adjustment (Tune) of the length of the coupled line sections.

Designing the complete biasing schematic (direct current) for both transistors (source voltage, decoupling capacitors, RF chokes) can bring you one extra point. The introduction of the bias components into the final schematic (with their parasitic elements and with additional 50 $\Omega$  connection lines and the modeling of possible transitions between the lines: figure 29) can bring an additional point.

For the sample assignment inserting the biasing components in the schematic from figure 29 decreases the gain below the minimum gain condition of 20dB in a restricted frequency range (figure 30). A final adjustment/optimization of the schematic (figure 31) provides the fulfillment of this criterion for the full bandwidth pf the amplifier (figure 32).

**Important Note 10.** Remember that the gain and noise requirements must be met (and checked) in the entire passband of the amplifier (figure 32), in the case of the current assignment in a 10% fractional

bandwidth (0.5GHz) around 5GHz. The final balancing across the entire amplifier passband usually **requires** the existence of the reserve/design margin initially provided at pt. 3.

Figure 31

The complete bonus (2p) for the bias schematic is obtained for the use of the complete low-level schematic for the transistor and the complete DC/AC simulation circuit (including resistive dividers, filtering capacitors, etc.) and might not be available for all transistors (you are restricted to the transistors types for which you can find the complete ADS model).

**Important Note 11.** The final grade will depend very much on the concentration while submitting the results. Regardless of the quality of the original design, if mistakes are made when filling out the data on the server, it is possible to have significant effects. For example, all 7 transmission lines in the amplifier schematic will have characteristic impedances of  $50\Omega$ , so the differences between the individual assignments will come from different and custom electrical lengths for these lines. For the lines (possibly coupled) in the filter diagram, most of the time the electrical lengths are  $90^{\circ}$  and the differences between the individual assignments will come from the different and custom characteristic impedances for these lines. A 50, 50, 50, 50, 50, 50, 90, 90, 90, 90, 90, 90, 90, 90, 90 submission (a clear confusion for all lines between characteristic impedance and electrical length) will not constitute a functional design so in most cases will not receive a passing grade.